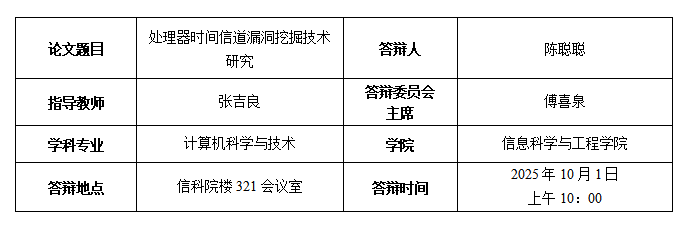

学位论文简介

现代处理器架构向高性能、高能效方向持续演进,但却引入一系列时间信道漏洞。这类漏洞突破了硬件隔离、操作系统权限与云环境租户等安全边界,使计算系统的安全性面临严重挑战。本文围绕这一主题,从手工分析和自动化检测两个方面,开展覆盖多层次、多组件的时间信道漏洞挖掘技术研究,为构建安全优先的新型计算架构提供理论支撑和技术工具,主要创新性研究成果如下:

(1) 发现延迟写技术和磁盘同步机制结合引入的安全风险,提出一组写隐蔽信道WRITE+SYNC,设计了基于同步文件和同步页面的多个隐蔽通信协议,并提出三种优化策略来提高信道的性能。评估了WRITE+SYNC在不同系统下的跨进程、跨沙盒泄露能力,并开发了网站指纹和性能下降等侧信道攻击。最后,讨论了相应的缓解策略,为操作系统级同步原语的安全设计提供参考。

(2) 发现惰性内存分配机制引入的安全风险,基于惰性分配特性和时间差异源分析,提出一组隐蔽信道LazyLeaks,设计多种基于只读共享内存方式实现的隐蔽信道协议。在不同系统的跨进程、跨沙盒场景下评估了LazyLeaks的泄露能力,实现了500 Kb/s的传输速率。最后讨论了相应的缓解策略,为操作系统内存管理安全提供新的解决方案。

(3) 分析了SIMD指令集资源共享引入的状态切换问题,基于寄存器状态切换和随机数生成过程引入的状态重置行为设计了三种隐蔽信道:MMX/X87、AVX/SSE和RDRAND/AVX,在多个商业处理器上评估了这些隐蔽信道的性能,实现了高达5.77 Mb/s的泄露速率,并验证了其与瞬态执行攻击结合的可行性。最后,讨论了相应的缓解策略,为向量化计算安全提供新见解。

(4) 针对现有黑盒漏洞挖掘方法覆盖面不足和挖掘效率不高的问题,提出一种基于模糊测试的自动化漏洞挖掘框架BETA。通过分析漏洞特征与指令组成,设计了一种自适应的突变算法,支持多种类型的漏洞覆盖;根据语义特征和硬件特性,提出一种指令分类方法,基于此设计了一种带覆盖率反馈的黑盒模糊测试算法,大幅提升模糊测试效率。BETA工具支持X86、ARM和RISC-V处理器架构,并发现了18个已知漏洞和8个新型时间信道漏洞,为未知漏洞的主动发现提供了可扩展的工具。

主要学术成果

[1] Congcong Chen, Jinhua Cui, Gang Qu, Jiliang Zhang. Write+Sync: Software Cache Write Covert Channels Exploiting Memory-Disk Synchronization [J]. IEEE Transactions on Information Forensics and Security, 2024, 19(1): 8066-8078. (SCI,第一作者)

[2] Congcong Chen, Chaoqun Shen, Jiliang Zhang. Lightweight and Secure Branch Predictors against Spectre Attacks [C]. 27th Asia and South Pacific Design Automation Conference, 2022: 25-30.(EI,第一作者)

[3] Jiliang Zhang, Congcong Chen, Jinhua Cui, Keqin Li. Timing Side-Channel Attacks and Countermeasures in CPU Microarchitectures [J]. ACM Computing Surveys, 2024, 56(7): 1-40. (SCI,导师一作,本人二作)

[4] Jinhua Cui, Yiyun Yin, Congcong Chen, Jiliang Zhang. Spoiler-Alert: Detecting Spoiler Attacks Using a Cuckoo Filter [C]. Design, Automation \& Test in Europe Conference \& Exhibition, 2023: 1-6. (EI)

[5] 张吉良,关振宇,陈卓俊,洪庆辉,陈聪聪,“基于物理不可克隆函数的安全分支预测器抗Spectre攻击方法”,已授权,专利号:ZL202210024761.5